Increased Efficiency in FPGA Arithmetic Operations

ID# 2013-4112

Technology Summary

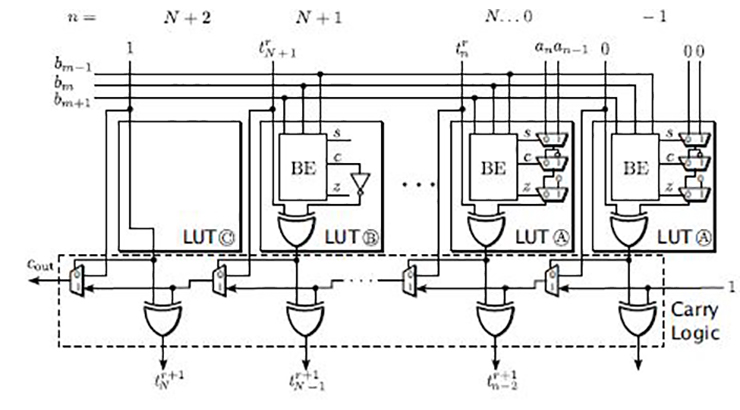

A field programmable gate array (FPGA) is used for computationally-intensive applications such as digital signal processing (DSP), video processing, image processing, and others. In these applications, multiplication is usually the dominant operation in terms of resource requirements, delay, and power consumption. Most modern FPGAs have embedded multipliers to deal with this issue, sometimes several thousand on one device. Unlike FPGA multipliers, LUT-based multipliers can be placed anywhere, their operands can be any size or type, and their number is limited only by the size of the FPGA. LUT-based multipliers are also used with embedded multipliers to make larger multipliers. This invention is a drop-in replacement for general-purpose or constant-coefficient multipliers in existing designs that would significantly improve many applications with little extra engineering effort.

Application & Market Utility

The disclosed LUT-based multipliers use significantly fewer resources (LUTs) and are faster than any known competing designs. They have been compared to Xilinx LogiCORE IP multipliers and use 32% to 52% fewer LUTs, have up to 22% less delay, and can increase throughput by up to 2.5 times for a fixed area on the FPGA. These advantages are gained through algorithm improvements and efficient usage of the 6-input LUT.

Next Steps

Fully developed. Seeking licensing oppurtunities. HDL Code for unsigned operands and operands with different bit widths can be developed quickly upon request.